清华新闻网3月5日电 近日,清华大学集成电路学院田禾副教授课题组和任天令教授团队等合作提出一种面向代工厂的二维芯片算法驱动的自适应优化制造策略,并基于此制备了基于二维材料的全互连微处理器。

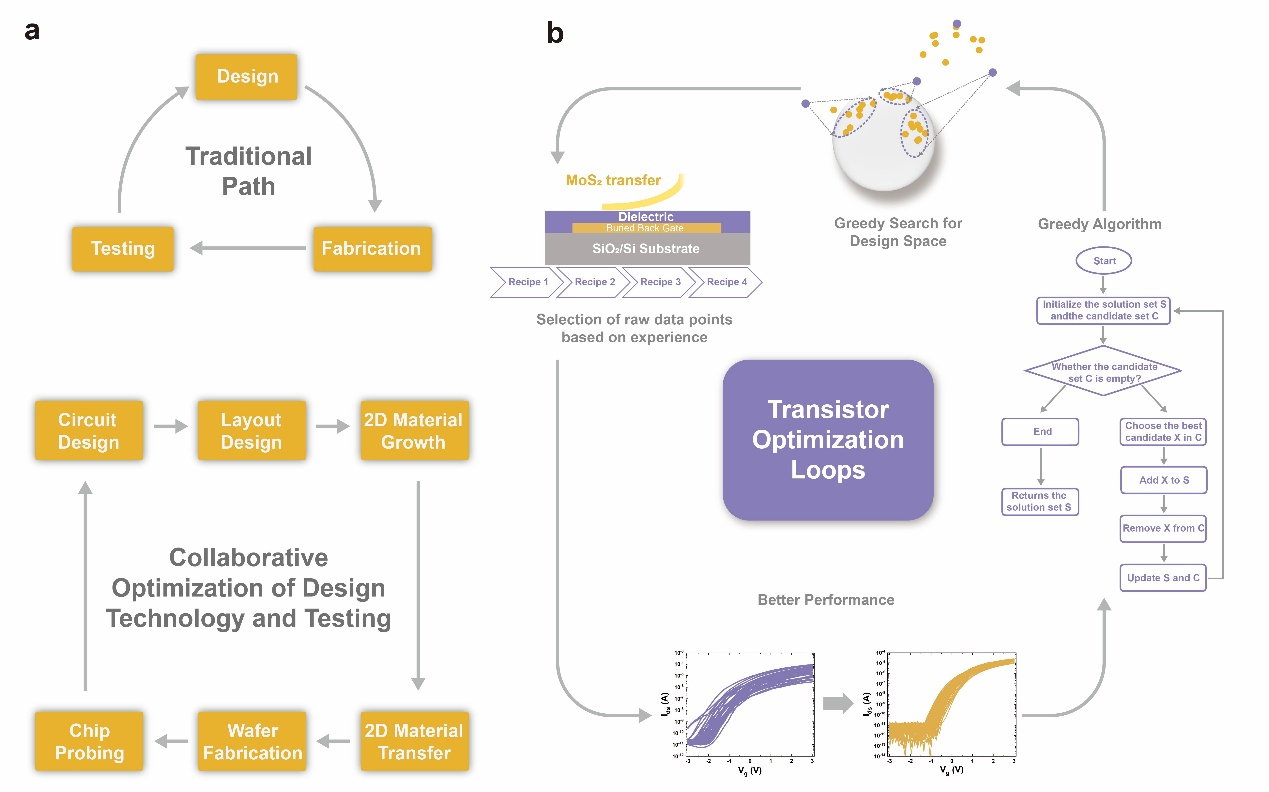

图1.面向代工厂策略与传统实验室制备工艺在芯片制造流程上的对比

硅场效应晶体管(FET)的特征尺寸正逼近其物理极限,而二维(2D)材料凭借其超大比表面积、高强度和高迁移率等特性,有望用于构建具备高集成度和多功能特征的更小器件。特别是过渡金属硫族化合物(TMDs)具有独特的晶体和能带结构,由此衍生出优异的物理性质:首先,其表面具有原子级平整度且无悬挂键,在作为晶体管导电沟道时能有效避免载流子声子散射导致的性能退化;其次,其厚度不足1纳米,极具器件微缩潜力,并能克服极端尺寸下的短沟道效应(SCEs)。

自基于二硫化钼(MoS2)晶体管实现反相器、与非门、静态随机存取存储器和五级环形振荡器以来,基于TMDs的电路已发展至包含数百个逻辑门的大规模演示,并涵盖了电流源、放大器、触发器和加法器等多种功能应用。这些器件通常采用转移法制备,使二维材料能兼容传统硅基工艺并应用于多层堆叠异质结构及柔性基底等不同场景。然而,基于转移的二维材料的大规模电路构建方面仍具挑战:与体材料的制造不同,单原子层沟道在材料转移、栅介质沉积和接触金属加工过程中极易退化,导致由此组成的大规模电路中多级信号传输后出现输出错误,降低芯片良率。

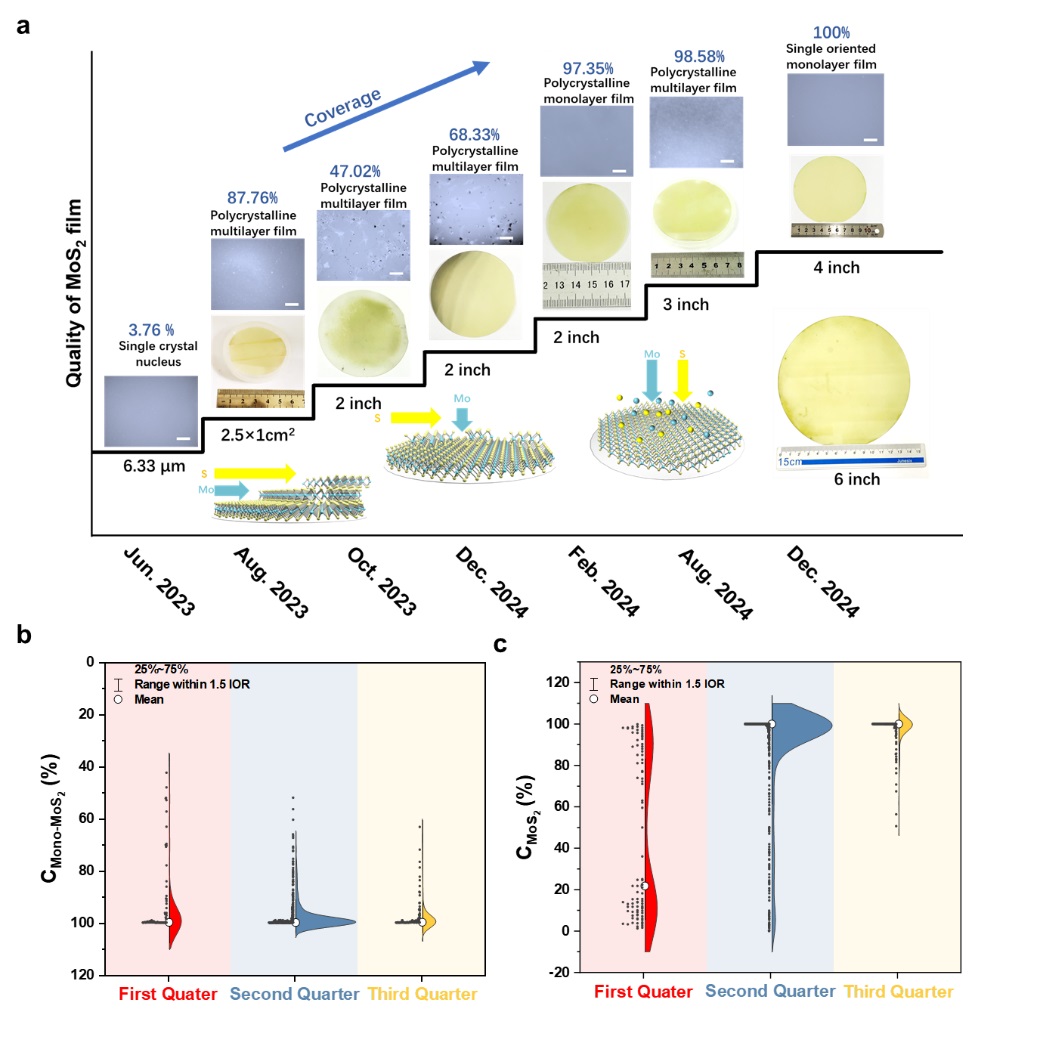

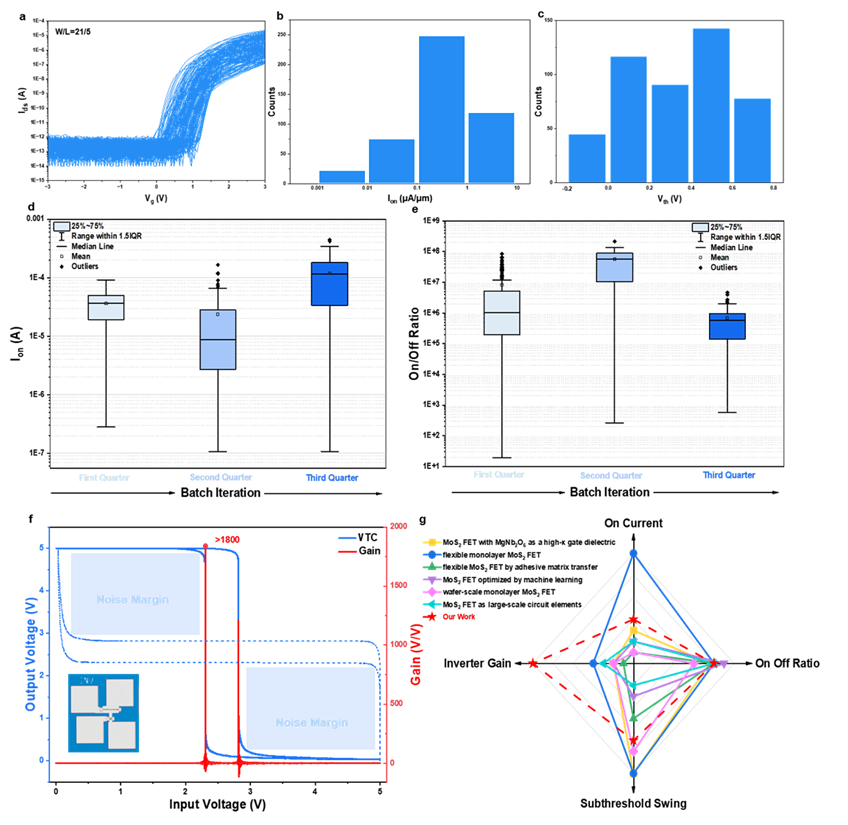

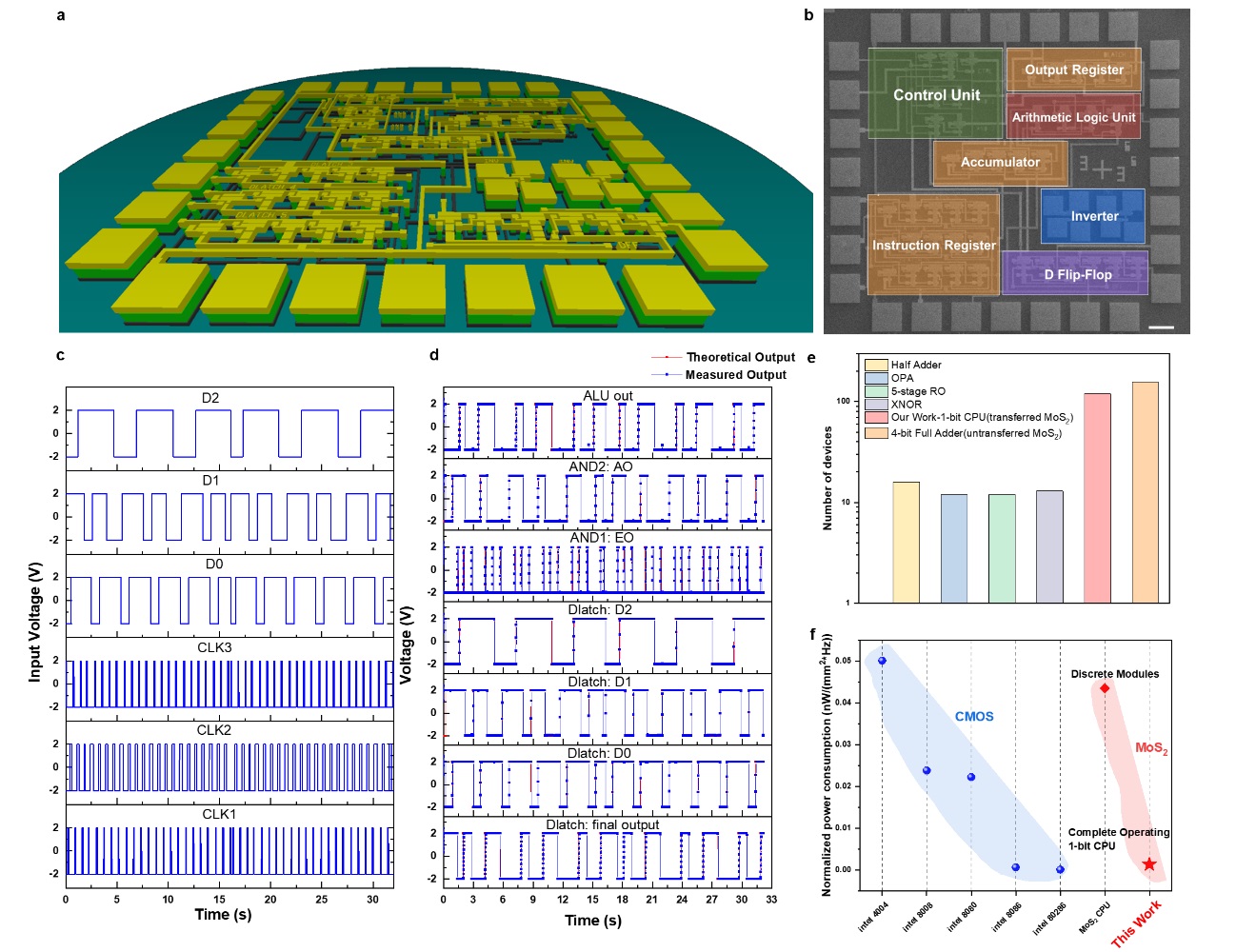

研究报告了一种专为二维材料电路定制的垂直整合制造(IDM)策略,该方法通过对电路设计、版图设计、二维材料生长与转移、器件加工及芯片测试的六个环节进行迭代优化,成功制造了全互连的二维处理器,并可拓展至不同功能、不同规模的二维电路中。通过持续优化单晶体管性能和模块良率,并整合材料、工艺与测试流程,本方法有效规避了常见的器件失效和均一性差等问题(图1)。在材料生长方面,本项目合作团队四川大学实现了从2英寸至4英寸二硫化钼(MoS2)材料的连续生长,薄膜在全域范围内保持了高度的均匀性与极佳的覆盖率(图2)。在单器件制造方面,研究团队实施了算法驱动的自适应优化方法,通过动态调整器件参数,实现了从晶体管的导通电流、开关比和亚阈值摆幅的全面提升,并实现了较高的平均反相器增益(图3)。在电路模块优化方面,基于全二维晶体管的算术逻辑单元(ALU)、控制单元(CU)及D锁存器良率分别达到96.5%、79.5%和61.5%。与Intel 4004和8008等第一代硅基中央处理器(CPU)相比,研究中的二硫化钼(MoS2)芯片展现出更低的归一化功耗、更佳的多材料系统兼容性以及更高的集成潜力(图4)。

图2. 晶圆级单层二硫化钼(MoS2)生长优化及其表征

图3.基于转移法的二硫化钼(MoS2)晶体管电学特性统计分析及反相器性能

图4.基于二硫化钼(MoS2)的全连接的中央处理器(CPU)及其与不同材料、规模的电路的对比

研究成果以“一种面向代工厂的二维全互连微处理器制造策略”(A towards-foundry strategy for creating fully interconnected two-dimensional microprocessors)为题,于2月26日在线发表于《自然·电子》(Nature Electronics)。

清华大学集成电路学院2024级博士生郭艺喆、2025级博士生张培根、2021级博士生刘晏铭、2024级硕士生刘志远、2022级博士生刘安晗和四川大学2025级博士生刘锦绣为论文共同第一作者,清华大学集成电路学院副教授田禾、教授任天令和四川大学教授王泽高为论文共同通讯作者。

研究得到国家自然科学基金委、北京市自然科学基金委、北京市自然科学基金-小米创新联合基金、清华-福州数据技术联合研究院、清华大学微纳加工中心、四川省科技计划项目和四川大学“双高计划”等的支持。

论文链接:

Https://doi.org/10.1038/s41928-026-01573-9

供稿:集成电路学院

编辑:李华山

审核:郭玲